Preface

Recently, some netizens said to the editor: Xilinx timing closure will not be used at all. I don't know what the tools are doing. I have been blindly looking at the report.

The good news is that Xilinx has released a new document ug1292. This document extracts the related content of timing closure in ug949 separately, and introduces the method of timing closure in the most concise language. ug1292 is a quick reference manual for timing closure, that is, after reading it, you can quickly know how to use tools to achieve timing closure.

UG1292 Baidu Cloud Link:

Link: https://pan.baidu.com/s/1FOZCRzDogrGeuIMDXkaeaA

Extraction code: gku9

ug1292 general understanding

This manual has only ten pages and can be read in one day. Each page has a flowchart or table to guide users to better operation. Each page of the manual is a chapter. If you don't understand any part, please turn to that page and read it carefully. It is recommended to read the original English version. The translation of the catalog is as follows:

Manual catalog

Page 1-Initial Design Check Process

Page 2-Timing Baseline Process

Page 3-Analyze the establishment of time violation process

Page 4-Keep time violation resolution

Page 5-Reduce logic delay flow

Pages 6, 7-Reduce network delay process

Page 8-Improve the clock skew process

Page 9-Improving the clock uncertainty process

Page 10-FAILFAST report overview

In fact, it can be seen from the catalog and content that xilinx's philosophy is to intervene in the early stages of design as much as possible for all problems. The more comprehensive the consideration at the initial stage of the design, the smoother the later work will be, that is, the timing is designed, not tested! So spend more time to design the timing in the early stage, and the progress may be slower at first, but many unnecessary problems will be avoided in the later stage. If the incomplete design in the early stage leads to the continuous patching of the later projects, the increase in maintenance costs will not justify the loss. Therefore, old drivers please be cautious in the early stage of the design. In the later stage, the various problems may not be solved at all. Even if it can be solved, the people who will take over the maintenance can only shout in their hearts: The concubines can't do it! !

At the beginning of the design period, timing issues can be considered from the following perspectives:

Initial design check

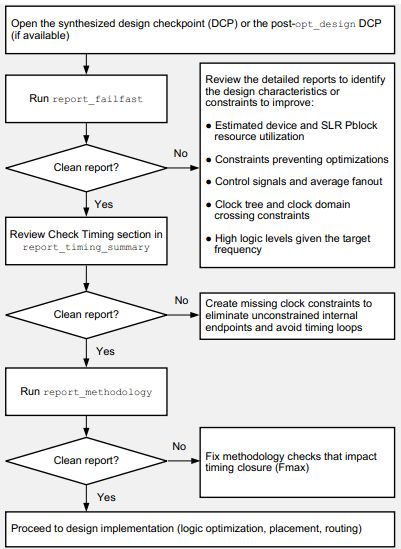

The first page of UG1292 is the instructions for use after synthesis or opt_design stage. The basic process of vivado has 5 steps (in fact, different strategies can be more, the specific usage and benefits will be discussed later), which are synth_design, opt_design, place_design, route_design, write_bitstream, each step can generate a timing report except for the final bit generation. Help analyze positioning problems or optimize design to provide guidance. The first page of UG1292 is about how to use the tools and reports provided by vivado to analyze and locate problems in the opt_design stage.

UG1292 initial design check flow chart

Simply put, only the following steps are required.

Initial design check steps

1. The dcp (design check point) generated in the opt_design phase

2. Use report_failfast to generate a failfast report

3. Use report_timing_summary to generate timing report

4. Use report_methodology to generate UFDM reports

Failfast report function

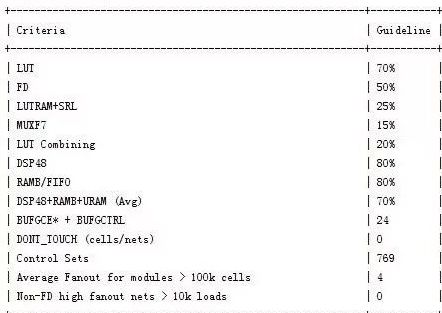

The function of failfast is to give the recommended upper limit and actual limit ratio of various resource utilization rates. According to the comparison of these two ratios, you can know where the timing bottleneck is, and you need to check it yourself. The following is the recommended utilization rate of each resource of a certain chip of K7:

If an actual usage index exceeds the guideline index, there will be REVIEW in the status column (there is no screenshot in the column next to the Guideline), which means that you need to check here. This will have a certain impact on the timing and you need to evaluate it manually. , But I don’t think it must be changed. For example, the recommendation of the DONT_TOUCH constraint is not to use one. However, in some special cases, people are sure to be better than the machine. Therefore, in order to prevent the compiler from modifying it, add this constraint, but the compiler is not sure whether you have it. Ability to grasp, or whether you have noticed this, so you will be prompted that if your design needs to be like this, and you are sure, then you don’t need to make any changes.

Timing report function

The timing report generated here does not make any sense in terms of path delays, because there is no place and route. The following points are mainly checked here.

Is there an unconstrained path under check_timing? Is there a loop? Is the constraint reasonable? For example, the actual constraint is 120M for a 125M clock.

Whether the path constraints of the asynchronous clock domain are reasonable.

UFDM report

The main function of UFDM (UltraFast Design Methodology) report is to report RTL-level code inspection, IP usage analysis and other aspects of the report, focusing on the Bad Practice items in the report.

HNB Cigarette

Shenzhen Uscool Technology Co., Ltd , https://www.uscoolvape.com