In practical applications, there may be a need for large matrix transpositions, especially for image applications where transposition is to achieve a 90° rotation of the image.

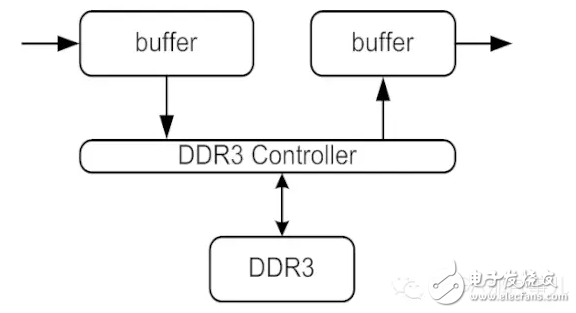

Since the RAM resources in the FPGA chip are generally insufficient to cache such large-scale matrix data, it is generally necessary to use external memory, generally DDR3. We need to organize the data into DDR3 in the direction of the row and then read the data in the direction of the column. So how to efficiently use the bandwidth of DDR3 is the core to achieve 90° flip of image matrix!

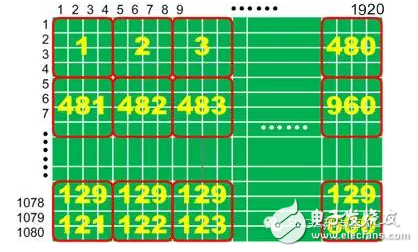

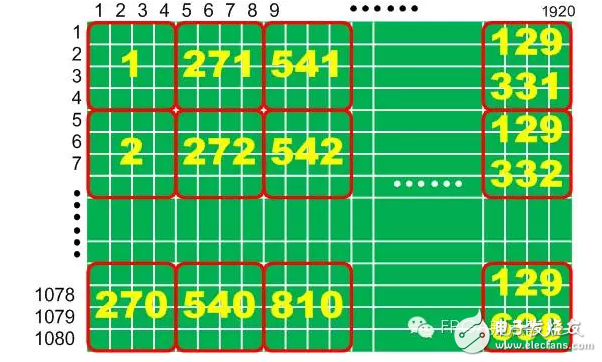

The following is a schematic diagram of a 1920x1080 matrix with access to DDR3. Both writing and reading are done in 4x4 blocks:

When writing, at least 4 lines of cache are required according to the following data organization:

When reading, according to the following data organization, at least 4 lines of cache are required:

Control Cable,Control Wire,Shielded Control Cable,Power Control Cable

HENAN QIFAN ELECTRIC CO., LTD. , https://www.hnqifancable.com